On Oct 31, we enjoyed a welcome party for laboratory new members, Associate Professor Matteo Convertino and Mr. Tian Yu.

Monthly Archives: November 2017

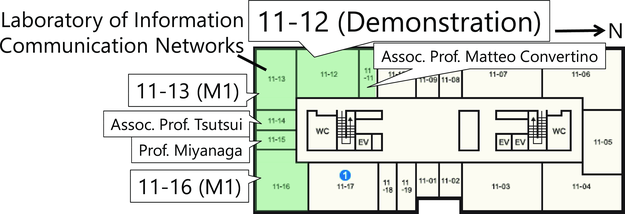

Lab tour for 3rd-year undergraduate students, 2017

Lab tour is available for 3rd-year undergraduate students.

- Venue: IST Building 11th floor 11-13

(Laboratory of Information Communication Networks) - Schedule: In the following time slots, M1 students are available for introducing our laboratory. The representatives of M1 students are Mr. Nakagoshi and Mr. Watanabe. We welcome your visit not limited to the following time slots.

- Nov. 8 (Wed) 16:30-18:00

- Nov. 9 (Thu) 16:30-18:00

- Nov. 10(Fri) 16:30-18:00 ← NEW!

- Nov. 13 (Mon) 16:30-18:00

The time slots of Wed and Thu overwrap the time of MN experiment II. Please come only if you completed your experiment task and you have time.

2017 Joint Convention, the Hokkaido Chapters of the Institutes of Electrical and Information Engineers

Mr. Watanabe presented his paper at 2017 Joint Convention, the Hokkaido Chapters of the Institutes of Electrical and Information Engineers, which was held at Future University Hakodate on Oct 28th-28th. In this paper, we presented an implementation approach to avoid memory conflicts of parallel processing to realize high throughput LDPC decoding.

- Taishi Watanabe, Takahiro Ikeshita, Hiroshi Tsutsui, Takashi Imagawa, Yoshikazu Miyanaga, “A Design of High-Throughput LDPC Min-Sum Decoder Using Parallelization,” Joint Conference of Electrical, Electronics and Information Engineers in Hokkaido, pp. 102-103, Oct. 2017 (in Japanese).

A student exchange meeting was held during this convention. Students of each university made presentations about their university, research activity, and student activity. Mr. Watanabe who is the member of IEEE student branch at Hokkaido university introduced the activity of the student branch.